# CHAPTER 7

# **POWER CIRCUIT DESIGN**

This chapter describes design of hybrid multilevel inverter. Single phase hybrid multilevel inverter is designed and is repeated for three phase. Regulated power supply is designed for 40 V and 80 V DC output. As discussed in previous chapter gating signals are applied through digital signal processor, buffer, isolation and driver.

## 7.1 DESIGN OF HYBRID MULTILEVEL INVERTER

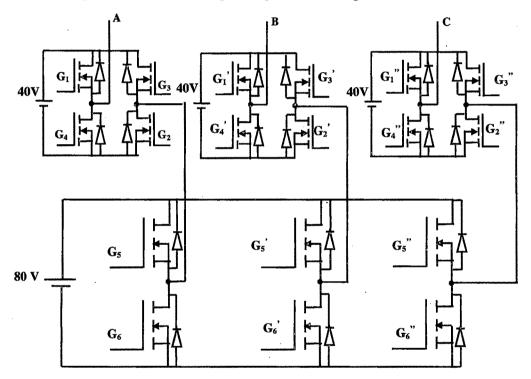

HMLI is designed for 110V, 5A rating. Gate pulse is obtained from circuit shown in previous chapter. MOSFET is chosen for high frequency switching, high voltage and high current operation. As shown in Fig. 7.1 separate DC voltages are connected.

# Fig. 7.1 Three phase hybrid multilevel inverter circuit diagram 7.1.1 DESIGN OF SINGLE AND THREE PHASE HYBRID MULTI LEVEL INVERTER

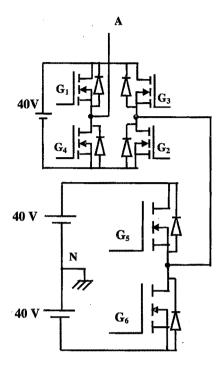

As shown in Fig 7.2 half bridge inverter is connected with H bridge inverter to form single leg of HMLI. As discussed switching is done at approximately 2.1 kHz frequency. Care is taken that switch has low saturation voltage and breakdown voltage is two to three times the supply voltage. Similarly for 3 phase such design is repeated.

# Fig. 7.2 Single leg of hybrid multilevel inverter circuit diagram

#### 7.1.2 MOSFET SELECTION

As circuit operates at 110V rms and 5A current MOSFET is chosen accordingly. IRF840N Power MOSFET is used. Features of IRF840 [1] are as follows:

-V<sub>DS</sub> 500V

-I<sub>D</sub> 8A(continuous)

-R<sub>DS</sub> (on) Low i.e 0.85  $\Omega$

-Exceptional dv/dt

-Low Gate Charge

-Application Oriented Characterization

- Low gate drive requirements

100K $\Omega$  resistance is connected as high impedance gate of MOSFET

K-1 type heat sink is used for MOSFET

#### 7.1.3 DESIGN OF MOSFET SNUBBER

An RC snubber, placed across each switch can be used to reduce the peak voltage at turn-off and to damp the ringing. Design for snubber is given below.

$f_s = 2 \text{ kHz}$

$Edc = 40 V, i_L=2A$

Let  $L = 25 \mu H$  $t_f = 66 \times 10^{-9} s$ where t<sub>f</sub> is fall time fs switching frequency  $C = i_{1,*}t_f / E_{dc}$  $= 6 * t_f / 40$  $C = 0.01 \mu F$  $L = E_{dc} * t_r / i_L$  $t_r = 1.26 \ \mu s$ where t<sub>r</sub> is rise time  $d_i/d_t = i_1/t_r$ = 1.58 A/µs Switch ON  $d_i/d_i = 0.395 \text{ A/}\mu\text{s}$  $R = \sqrt{4*L/C}$  $R = 100 \Omega$

Hence values for snubber are chosen as 100  $\Omega$ ,1W and 0.01 $\mu$ F/400V.

#### 7.2 DESIGN OF REGULATED POWER SUPPLY

Step down transformers of rating 230V/45V and 230V/70V are used to obtain 40V and 80V DC respectively from voltage regulator. Current rating is 5A as design is for 110V rms from output with 5A current.

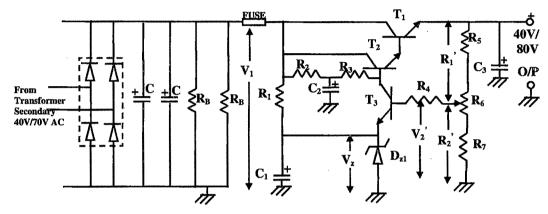

Controlled transistor series regulator circuit is designed and implemented as shown in Fig. 7.3 Components are chosen as per requirement. Selection of transistors  $T_1$ ,  $T_2$ ,  $T_3$  is done on basis of  $V_{CEO}$ , gain and power rating from datasheet [2-5]. Due to high power dissipation heat sink is included in circuit.

Working principle can be explained as follows: Unregulated DC voltage is passed through filter capacitor C and bleeder resistances  $R_B$  and as per change in output load current regulation is obtained from regulator circuit. If current through load increases drop across  $R_6$  increases which increases base current of  $T_3$  thus increasing collector current of  $T_3$ , which increases base current of  $T_1$  through  $T_2$  thus finally reducing emitter current of  $T_1$  and regulating output current and voltage.  $R_2$ ,  $R_3$  and  $C_2$  form filter and current limiting path for  $T_3$ . Zener diode gives minimum emitter voltage of  $T_3$  with  $C_1$  as filter for zener diode. Component choice is done as per requirement. Darlington pair of transistor  $T_1$  and  $T_2$  is control element and is called pass transistor as all load current flows through it. Zener diode and resistor  $R_1$  act as reference element. The voltage divider  $R_5$ ,  $R_6$ , and  $R_7$  samples output voltage and delivers a negative feedback voltage to the base of transistor  $T_3$  [6]. Design and practical readings for regulated power supply are given in Appendix A. While hardware setup is given in appendix B.

Fig. 7.3 Regulated power supply

| Component                         | Value                            |

|-----------------------------------|----------------------------------|

| R <sub>1</sub>                    | 10 kΩ/1W22 kΩ/2W(for 80V)        |

| R <sub>2</sub>                    | 470 Ω/0.5W                       |

| R <sub>3</sub>                    | 1 kΩ/0.5W                        |

| R <sub>4</sub>                    | 100 Ω/0.25W                      |

| R <sub>5</sub>                    | 6.2 kΩ10 KΩ(for 80V)             |

| R <sub>6</sub>                    | $500 \Omega$ preset              |

| R <sub>7</sub>                    | 1 kΩ                             |

| <b>C</b> <sub>1</sub>             | 100 μF/16V                       |

| C <sub>2</sub>                    | 47μF/63V47μF/160V                |

| C <sub>3</sub>                    | 100µF/63V                        |

| D <sub>z1</sub>                   | 6.2V/1W                          |

| T <sub>1</sub>                    | 2N37732N3773(for 80V)            |

| T <sub>2</sub>                    | 2N35012N3773(for 80V)            |

| T <sub>3</sub>                    | BD139TIP122                      |

| Bridge rectifier 3510             | 35 A, 1000V                      |

| Bleeder resistance R <sub>B</sub> | 1 kΩ/10W2.2 kΩ/10W(for 80V)      |

| Filter capacitor C                | 4700 μF/100V1800μF/160V(for 80V) |

**Table 7.1 Component list**

### 7.3 SUMMARY

In this chapter power circuit design is explained. Linear regulated power supply is also designed and its design is discussed. Hybrid multilevel inverter is designed. MOSFET switches were selected on design basis. Heat sink is selected as per dissipation. R-C snubber is also designed.