# **CHAPTER 8**

# **EXPERIMENTAL RESULTS**

#### **Experimental Results**

In this chapter, results obtained from hardware implementation are compared with simulation results for selected scheme. Comparison is on basis of THD, output voltage obtained and fundamental voltage from FFT analysis. Hardware testing is done with lower as well as higher voltage. For lower voltage 12V batteries are taken as supply for single phase as well as three phase. Initially single leg is tested with and without modulation. Similar three cards are made and tested individually then three phase connections are done. In three phase output is obtained for different modulation techniques which have been already discussed in previous chapters. Modulation index is taken either 0.9 while frequency modulation index is 21.Control signals are applied using SIMULINK-CCS3.1-EMULATOR C2000 USB- DSP KIT 28335 as discussed in chapter 6.

Output is saved in DSO in .bmp and .csv extension. The file saved in .csv format is imported in MATLAB R2013a and then THD is found. Limitations of this method are: i) maximum 1024 points are saved ii) first half cycle output reconstructed from such points is not proper iii) maximum two cycles are obtained from points saved in .csv format.

Further sections describe different outputs for various ratings of voltage and current with different gating pulses for selected configuration of single phase and three phase HMLI.

# 8.1 HARDWARE RESULTS FOR SINGLE PHASE HYBRID MULTILEVEL INVERTER

Single phase hybrid multilevel inverter is tested on 12V batteries and respective five level output is obtained. Output is taken for R and R-L load.

#### 8.1.1 HARDWARE OUTPUT FOR SINGLE PHASE HMLI WITHOUT MODULATION

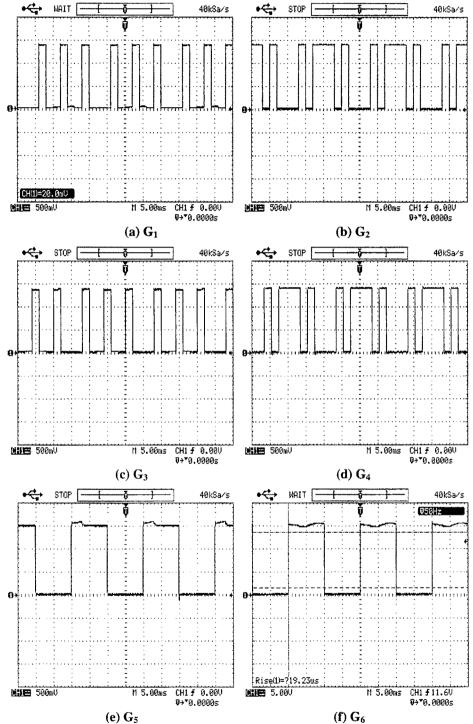

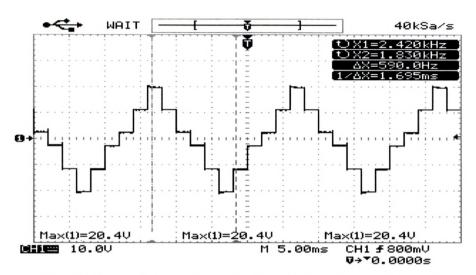

Fig 8.1 shows control signals for six switches. Fig 8.2 shows five level output 220  $\Omega$ -1/2 Watt resistor connected as load. Fig. 8.3 is THD obtained from .csv file imported to MATLAB.

Fig. 8.1 Control signals for single phase HMLI without modulation

Fig. 8.2 Five level output for single phase HMLI without modulation

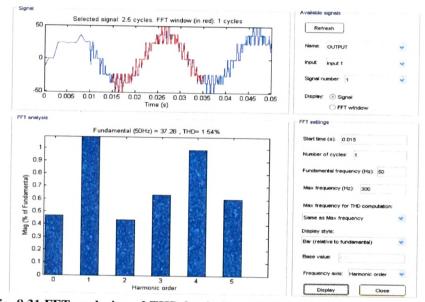

# Fig. 8.3 FFT analysis and THD for single phase HMLI without modulation 8.1.2 HARDWARE OUTPUT FOR SINGLE PHASE HMLI WITH PD MODULATION TECHNIQUE

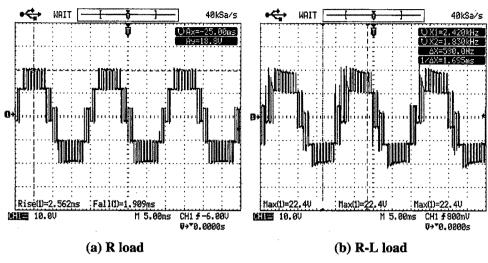

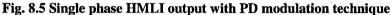

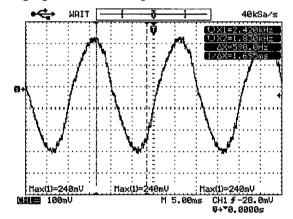

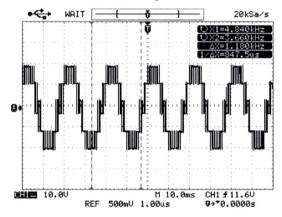

Fig 8.4 shows control signals for six switches. Fig 8.5 (a) shows five level output across 220  $\Omega$ - 1 Watt resistive load. Fig 8.5 (b) shows five level output across R-L load. Fig. 8.6 shows current through RL load for single phase HMLI with PD modulation technique. Fig 8.7 (a) is five level output with FFT for R load as mentioned above. Control signals are given at sample rate of 10 kHz which is changed to 100 kHz for better resolution as shown in Fig 8.7 (b). Fig. 8.8 is THD obtained from .csv file imported to MATLAB. Fig. 8.9 shows similar output for second card.

#### **Experimental Results**

Fig. 8.4 Control signals for single phase HMLI with PD modulation technique

#### **Experimental Results**

Fig. 8.6 Current through RL load for single phase HMLI with PD modulation technique

Fig. 8.7 Single phase HMLI output and FFT with PD modulation technique for R load

#### **Experimental Results**

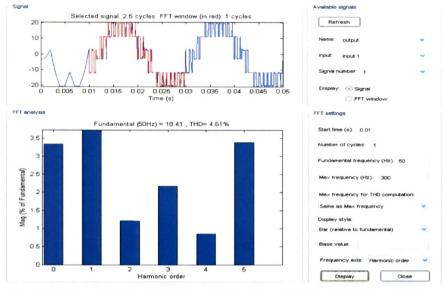

Fig. 8.8 FFT analysis and THD for single phase HMLI with PD modulation technique

# Fig. 8.9 Single phase HMLI output with PD modulation technique for R load

# 8.2 HARDWARE RESULTS FOR THREE PHASE HYBRID MULTILEVEL INVERTER

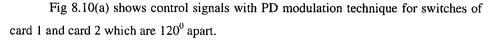

Three phase hybrid multilevel inverter is tested on 12V batteries and as discussed in chapter 7 DC supply for three phase inverter is double the H bridge supply hence two batteries in series are connected. Testing is also done with regulated power supplies of value 80V and 40V. Output is measured across resistive load in star configuration. Control signals are phase shifted by  $120^{\circ}$ . Different modulation techniques are applied.

## 8.2.1 HARDWARE OUTPUT FOR THREE PHASE HMLI WITH PD MODULATION TECHNIQUE

#### i) BATTERIES AS SUPPLY

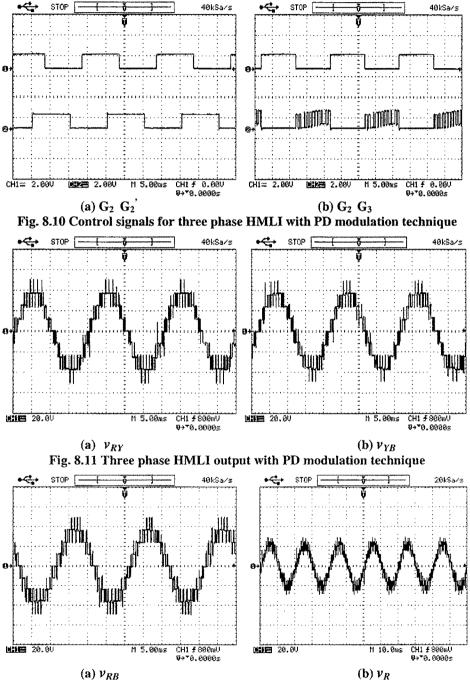

Fig. 8.12 Three phase HMLI output with PD modulation technique

#### **Experimental Results**

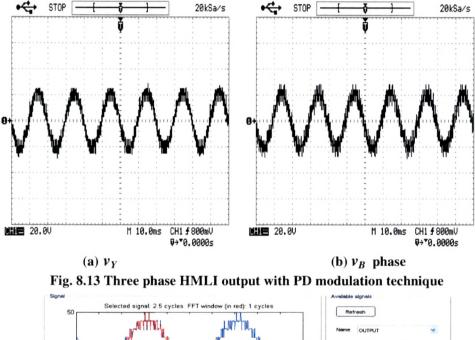

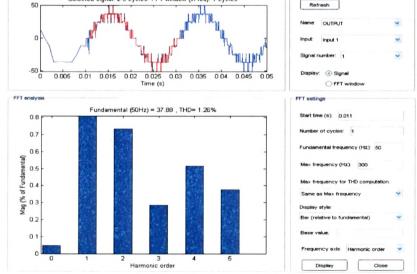

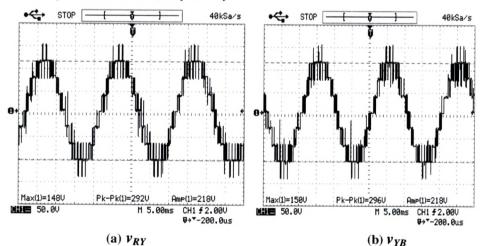

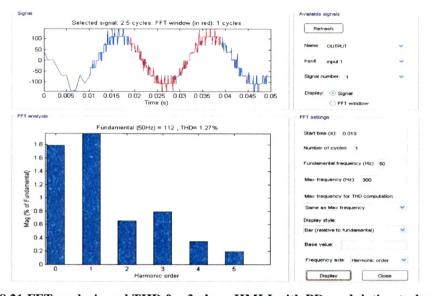

Fig 8.11(a) shows 9 level line to line output voltage( $v_{RY}$ ). 100  $\Omega$ -1W resistors are star connected as load. Fig 8.11(b) output voltage  $v_{YB}$ . Fig 8.12 (a) output voltage  $v_{RB}$ . Fig 8.12(b) shows 7 level  $v_R$  output voltage while Fig 8.13(a) and (b) shows 7 level output voltage  $v_Y$  and  $v_B$  respectively. Control signals were given at sample rate of 25 kHz due to limitation of MATLAB SIMULINK. Fig. 8.14 shows THD obtained from .csv file imported to MATLAB for one output and other values are mentioned in Table 8.1.

Fig. 8.14 FFT analysis and THD for 3 phase HMLI with PD modulation technique

#### ii) REGULATED POWER SUPPLY

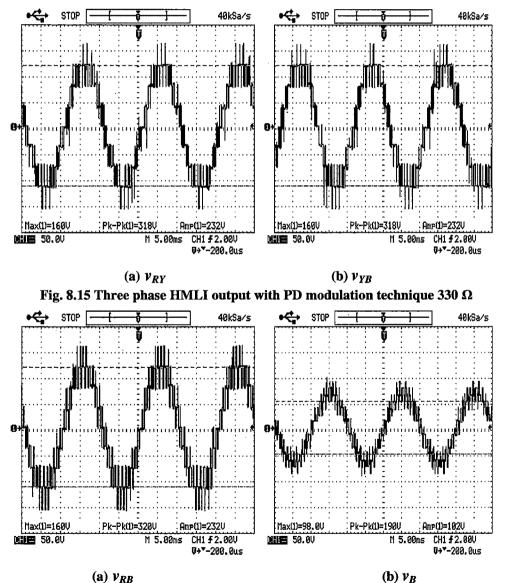

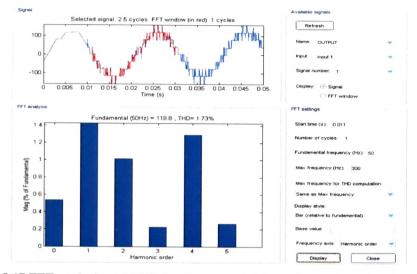

Fig 8.15(a) and (b) shows 9 level line to line output voltage  $v_{RY}$  and  $v_{YB}$  respectively. Three 1 k $\Omega$ - 10 W resistors are connected in parallel to obtain equivalent resistor of 330  $\Omega$  which are star connected as load. Fig 8.16 (a) output voltage  $v_{RB}$  and Fig 8.16 (b) shows 7 level  $v_B$  phase output voltage. Control signals were given at sample rate of 25 kHz due to limitation of MATLAB SIMULINK. Fig. 8.17 is THD obtained from .csv file imported to MATLAB for one output and other values are mentioned in Table 8.1.

Fig. 8.16 Three phase HMLI output with PD modulation technique 330  $\Omega$

#### **Experimental Results**

Fig. 8.17 FFT analysis and THD for three phase Line to line voltage for RY 330Ω star load

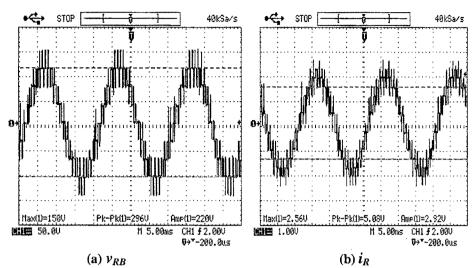

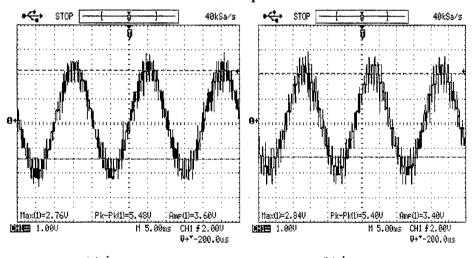

Fig 8.18 (a) shows 9 level line to line output voltage( $v_{RY}$ ). 33 $\Omega$ - 1000 W heater coil are star connected as load. Fig 8.18 (b) shows output voltage  $v_{YB}$ . Fig 8.19 (a) shows output voltage  $v_{RB}$ . Control signals were given at sample rate of 25 KHz due to limitation MATLAB SIMULINK. Fig. 8.21 is THD obtained from .csv file imported to MATLAB for one output and other values are mentioned in Table 8.1. Fig. 8.19 (b) shows output current  $i_R$  measured across 1 $\Omega$  resistor connected in series with load. Fig. 8.20(a) and (b) show output current  $i_Y$  and  $i_B$  respectively.

Fig. 8.18 Three phase HMLI output with PD modulation technique  $33\Omega$

Fig. 8.19 Output voltage and current for Three phase HMLI with PD modulation technique

(a)  $\dot{i}_Y$  (b)  $\dot{i}_B$ Fig. 8.20 Output current for three phase HMLI with PD modulation

**Experimental Results**

# Fig. 8.21 FFT analysis and THD for 3 phase HMLI with PD modulation technique 8.2.2 HARDWARE OUTPUT FOR THREE PHASE HMLI WITH POD MODULATION TECHNIQUE

## i) BATTERIES AS SUPPLY

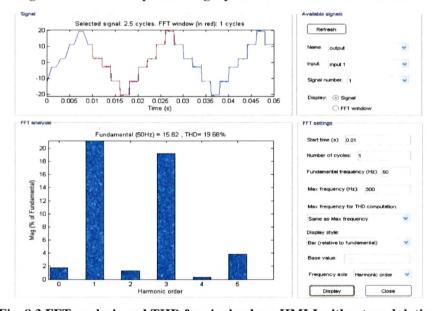

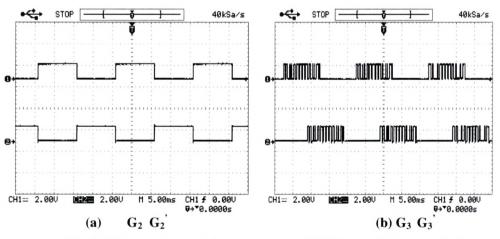

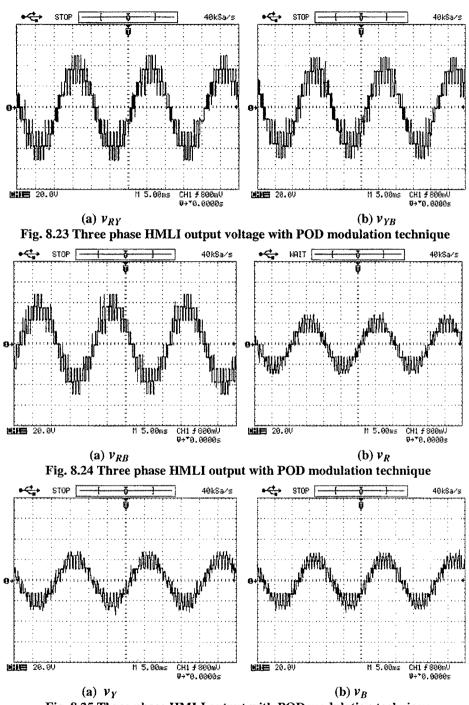

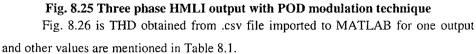

Fig 8.22(b) shows control signals with POD modulation technique for switches of card 1 and card 2 which are  $120^{0}$  apart. Fig 8.23(a) shows 9 level line to line output voltage( $v_{RY}$ ). 100  $\Omega$ - 1 W resistors are star connected as load. Fig 8.23(b) shows output line voltage. Fig 8.24 (a) output voltage  $v_{RB}$ . Fig 8.24 (b) shows 7 level  $v_R$  phase output voltage while Fig 8.25 (a) and (b) show 7 level phase voltage  $v_Y$  and  $v_B$  respectively. Control signals were given at sample rate of 25 kHz due to limitation of MATLAB SIMULINK.

Fig. 8.22 Control signals for three phase HMLI with POD modulation technique

#### **Experimental Results**

# Fig. 8.26 FFT analysis and THD for 3 phase HMLI with POD modulation technique 8.2.3 HARDWARE OUTPUT FOR THREE PHASE HMLI WITH APOD MODULATION TECHNIQUE

#### i) BATTERIES AS SUPPLY

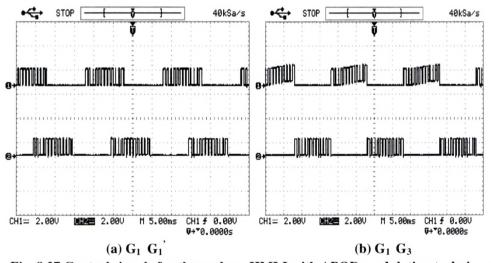

Fig 8.27(a) shows control signals with APOD modulation technique for switches which are  $120^{0}$  apart.

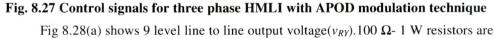

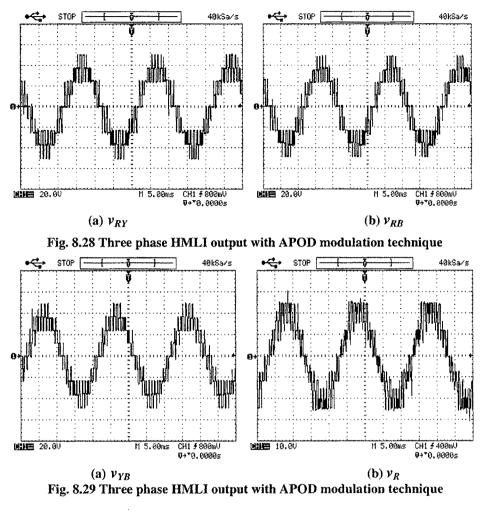

star connected as load. Fig 8.28(b) output voltage  $v_{YB}$ . Fig 8.29(a) output voltage  $v_{RB}$

Fig. 8.30 Three phase HMLI output with APOD modulation technique

139

#### **Experimental Results**

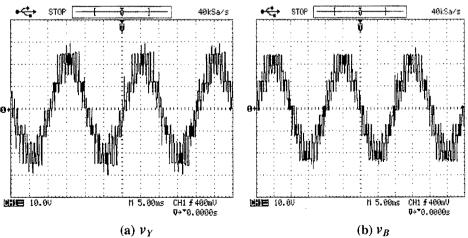

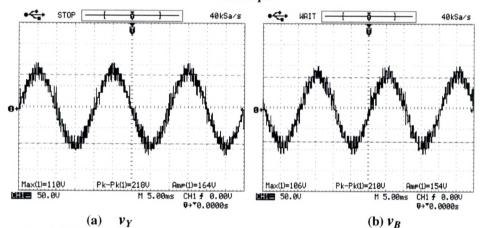

. Fig 8.29(b) shows 7 level  $v_R$  phase output voltage while Fig 8.30 (a) and (b) show 7 level output voltages  $v_Y$  and  $v_B$  respectively. Control signals were given at sample rate of 25 kHz due to limitation of MATLAB SIMULINK. Fig. 8.31 is THD obtained from .csv file imported to MATLAB for one output and other values are mentioned in Table 8.1.

Fig. 8.31 FFT analysis and THD for 3 phase HMLI with APOD modulation technique

# 8.2.4 HARDWARE OUTPUT FOR THREE PHASE HMLI WITH THIRD HARMONIC MODULATION TECHNIQUE (PD)

## i) BATTERIES AS SUPPLY

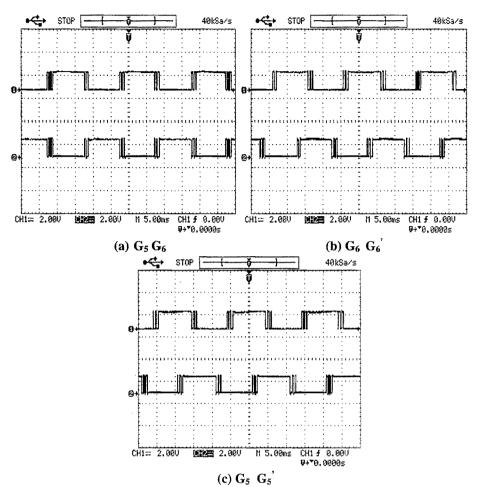

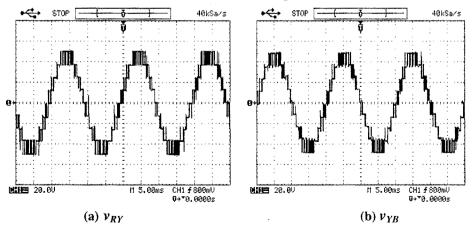

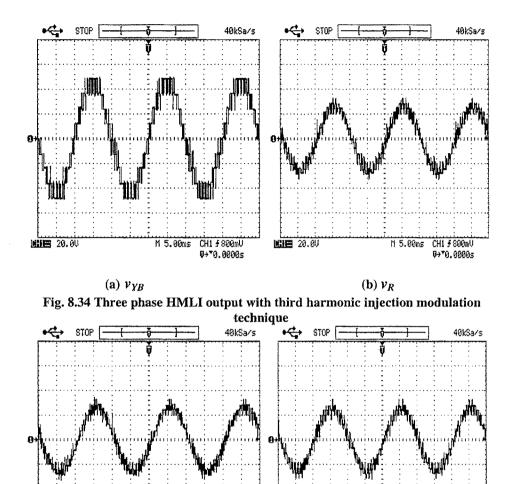

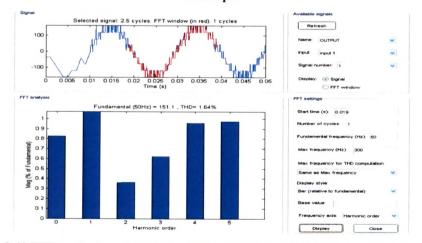

Fig 8.32(b) shows control signals with third harmonic injection modulation technique for switches which are  $120^{0}$  apart. Fig 8.33(a) shows 9 level line to line output voltage( $v_{RY}$ ). 100  $\Omega$ - 1 W resistors are star connected as load. Fig 8.33(b) shows output voltage  $v_{YB}$ . Fig 8.34(a) is output voltage  $v_{RB}$ . Fig 8.34(b) shows 7 level  $v_R$  phase output voltage while Fig 8.35(a) and (b) show 7 level output voltage  $v_Y$  and  $v_B$  respectively. Control signals were given at sample rate of 25 kHz due to limitation of MATLAB SIMULINK. Fig. 8.36 is THD obtained from .csv file imported to MATLAB for one output and other values are mentioned in Table 8.1.

Fig. 8.32 Control signals for three phase HMLI with third harmonic injection modulation technique

Fig. 8.33 Three phase HMLI output with third harmonic injection modulation technique

118 20.0V

CH1 £800mV V→™0.0000s

CHE 20.0V

Fig. 8.35 Three phase HMLI output with third harmonic injection modulation technique

M 5.00ms

(a)  $v_Y$

142

CH1 £300mU \$+\*0.0000s

M 5.00ms

(b)  $v_B$

#### **Experimental Results**

#### **Chapter 8**

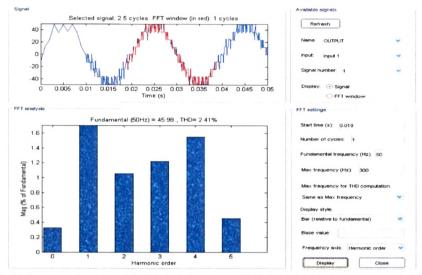

Fig. 8.36 FFT analysis and THD for 3 phase HMLI with third harmonic injection modulation technique Y-B

## ii) REGULATED POWER SUPPLY

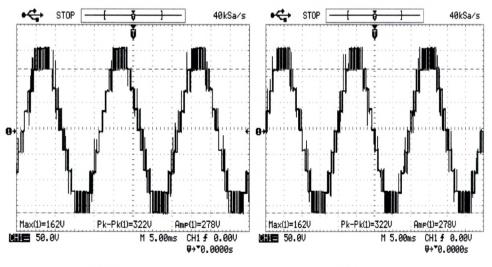

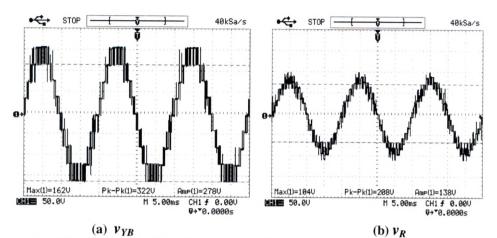

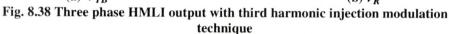

Fig 8.37(a) shows 9 level line to line output voltage  $(v_{RY})$ . 1 k $\Omega$ - 10 W resistors are star connected as load. Fig 8.37(b) output voltage  $v_{YB}$ . Fig 8.38(a) output voltage  $v_{RB}$ . Fig 8.38(b) shows 7 level  $v_R$  output voltage while Fig 8.39(a) and (b) show 7 level output voltage  $v_Y$  and  $v_B$  respectively. Control signals were given at sample rate of 25 kHz due to limitation of MATLAB SIMULINK. Fig. 8.40 is THD obtained from .csv file imported to MATLAB for one output and other values are mentioned in Table 8.1.

(a)  $v_{RY}$  (b)  $v_{RB}$ Fig. 8.37 Three phase HMLI output with third harmonic injection modulation technique

Fig. 8.39 Three phase HMLI output with third harmonic injection modulation technique

Fig. 8.40 FFT analysis and THD for 3 phase HMLI with third harmonic injection modulation technique

# **Experimental Results**

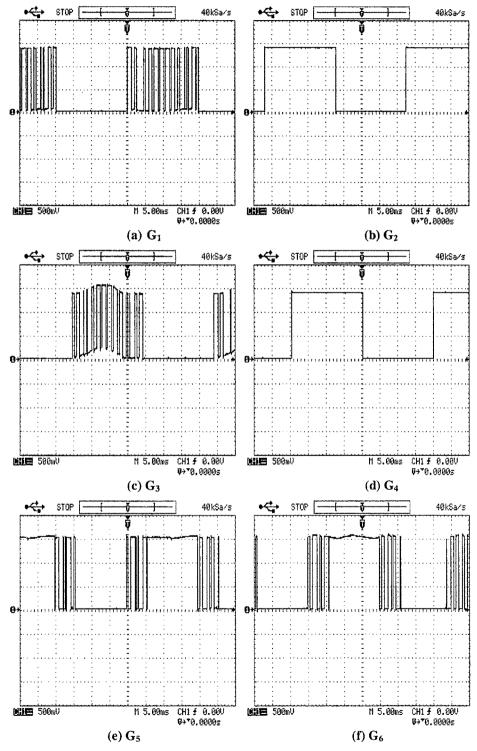

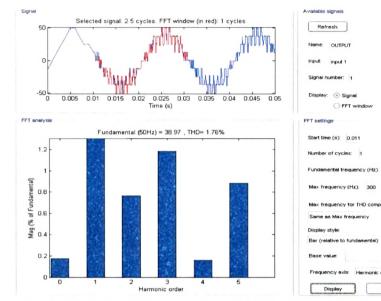

|  | Modulation<br>Technique        | Line to line<br>voltage | DC input in<br>Volts | Start Time | Simulation<br>Results |       |              | Hardware<br>Results |               |                  |           |

|--|--------------------------------|-------------------------|----------------------|------------|-----------------------|-------|--------------|---------------------|---------------|------------------|-----------|

|  |                                |                         |                      |            | V <sub>o</sub>        | V1    | 7<br>THD     | Va                  | load $\Omega$ | $\mathbf{v}_{i}$ | 70<br>THD |

|  | PD                             | V <sub>RY</sub>         | 24-<br>12            | .01/.011   | 96                    | 41.64 | 0.59         | 90                  | 100           | 37.88            | 1.26      |

|  |                                | V <sub>YB</sub>         |                      | .01        | 96                    | 41.5  | 0.74         | 90                  | 100           | 37.09            | 1.95      |

|  |                                | V <sub>BR</sub>         |                      | .01/.027   | 96                    | 41.64 | 0.53         | 90                  | 100           | 37               | 2.48      |

|  |                                | V <sub>RY</sub>         | 80-<br>40            |            |                       |       |              | 316                 | 330           | 119.8            | 1.73      |

|  |                                | VYB                     |                      |            |                       |       |              | 320                 | 330           | 119.5            | 1.8       |

|  |                                | V <sub>RY</sub>         | 80-<br>40            | .02/.019   | 320                   | 138.5 | 0.49         | 292                 | 33            | 112              | 1.27      |

|  |                                | V <sub>BR</sub>         |                      | .02/.029   | 320                   | 138.5 | 0.45         | 296                 | 33            | 113.1            | 1.38      |

|  |                                | V <sub>YB</sub>         |                      | .02/.029   | 320                   | 138.5 | 0.53         | 296                 | 33            | 111.6            | 1.35      |

|  | POD                            | V <sub>RY</sub>         | 24-<br>12            | .01/.011   | 96                    | 41.52 | 0.49         | 96                  | 100           | 38.97            | 1.76      |

|  |                                | V <sub>YB</sub>         |                      | .012       | 96                    | 41.56 | 0.58         |                     | 100           |                  |           |

|  |                                | V <sub>BR</sub>         |                      | .017       | 96                    | 41.57 | 0.65         | 96                  | 100           | 38.28            | 1.58      |

|  | APOD                           | V <sub>RY</sub>         | 24-<br>12            | .015       |                       | 41.57 | 0.19         | 96                  | 100           | 37.28            | 1.54      |

|  |                                | V <sub>YB</sub>         |                      | .015/.01   |                       | 41.58 | 0.37/.<br>87 | 96                  | 100           | 36.76            | 1.82      |

|  |                                | V <sub>BR</sub>         |                      | .01/.02    |                       | 41.53 | .18/.6<br>3  | 96                  | 100           | 36.82            | 1.72      |

|  | Third<br>Harmonic<br>Injection | V <sub>RY</sub>         | 24-<br>12            | .01        | 96                    | 45.86 | 2.14         | 96                  | 100           | 46.57            | 2.44      |

|  |                                | V <sub>YB</sub>         |                      | .019       | 96                    | 45.43 | 1.96         | 96                  | 100           | 45.98            | 2.41      |

|  |                                | V <sub>BR</sub>         |                      | .015       | 96                    | 45.82 | 2.37         | 96                  | 100           | 46.13            | 2.52      |

|  |                                | V <sub>RY</sub>         | 80-<br>40            | .019/.02   | 320                   | 152.6 | 1.51         | 322                 | lk            | 148.6            | 1.65      |

|  |                                | VYB                     |                      | .019/.017  | 320                   | 153   | 1.77         | 322                 | lk            | 1:50.4           | 2.06      |

|  |                                | V <sub>BR</sub>         |                      | .019/.019  | 320                   | 152.6 | 1.51         | 322                 | lk            | 151.1            | 1.64      |

|  | PD                             | vo                      | 12-<br>12-<br>12     | .01        | 48                    | 24    | 0.79         | 40                  | 100           | 18.41            | 4.61      |

Table 8.1 Summary of output

.

Number of cycles for THD----1

Output levels for 3 phase----9

#### **Experimental Results**

#### **Chapter 8**

V<sub>1</sub>----Fundamental voltage

Vo----Peak to peak output voltage in volts

THD noted at maximum frequency as 300Hz.

vo----Single phase output

# 8.3 SUMMARY

In this chapter hardware results are given. Hardware was tested at low voltage battery and high voltage regulated power supply. Results were compared for low and high voltage for different modulation techniques. It is observed that there is no much difference in THD as voltage is increased from low to high.

It is observed that with PD modulation technique THD obtained from simulation much more less with respect to THD obtained from hardware results for low as well as high DC voltage applied. POD and APOD modulation techniques are implemented for low DC voltage. Variation in THD is more for APOD modulation technique when simulated and applied for hardware as compared to POD modulation technique results.

It was expected that THD would be less for third harmonic injection modulation technique as compared to other modulation techniques, but practically THD is more.